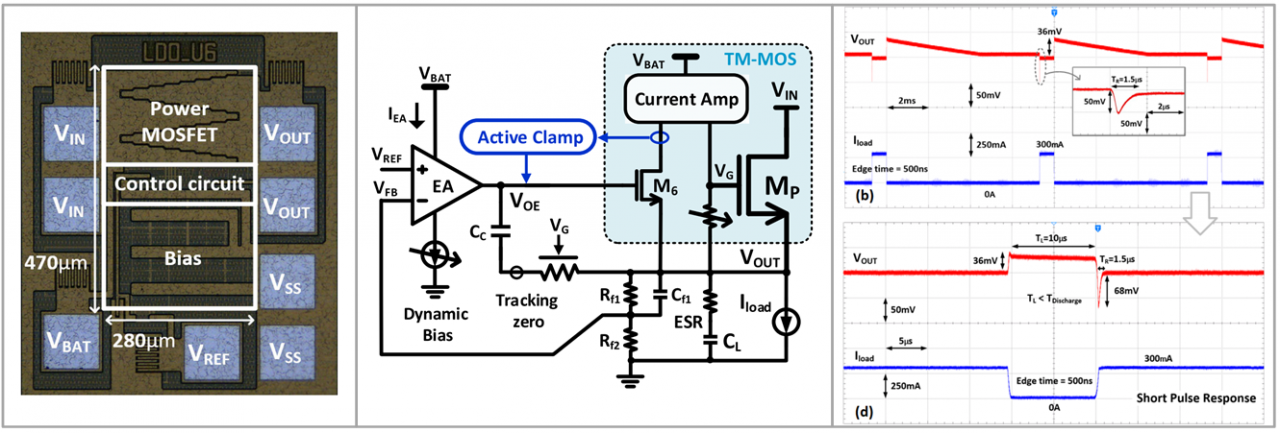

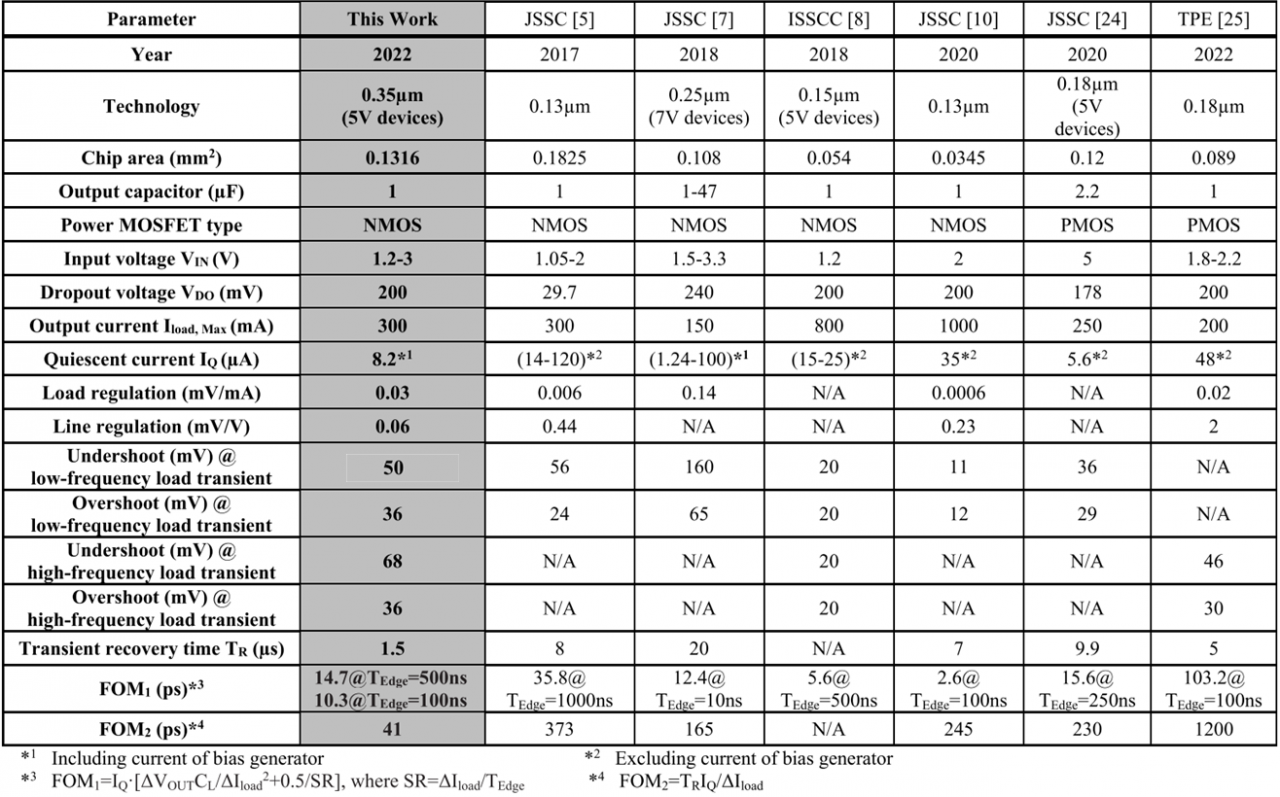

ԓ헼��g���@�����������֙C�͟o�˙C�ȸ����������ܣ��������M��ؓ�d������պ���Դ�Qλ���Ƽܘ����o�B���ăH��8.2��A����ͬ�r̎���ߵ��lؓ�d˲�B��׃����LDO˲�BƷ�|��Figure-of-merit, FoM�����s��41ps���״Ό��F�����LDO�I�������l���d������10��s�g���������ν��ڞ��һ/ͨӍ���ߣ�ָ���ĴTʿ�о�������܊��ڶ����ߡ�

�Ƅ��O��һ������늳أ�3.6-4.5V������·Buck׃�Q��+LDO���cʽ��늼ܘ���Buck���ڸ�Ч�ʽ�������LDO��Buckݔ���y��늉��D�Q�鷀������Դ��LDO�OӋ���R�P�I���𣺣�1������Flash Memory��ݔ��늉��^�ͣ�VIN=1V����ؓ�d����^��Iload>300mA���đ��ã�LDOͨ������N���ʹ܁�pСоƬ��e�Լ�����˲�B���ܡ�����NMOS-LDO���е������^���}�����lؓ�d��׃���@������˲�B���ܣ���2��LDO���o�B������Ҫ��С�������L늳�ʹ�Õr�g��Ȼ�������ĵ�����LDO��˲�B���Դ���Ʊȵ��P�I���ܡ�

���������������ν����о�С�M�о��OӋ��һ�N�o�B������ա����������^��LDO���Ƽܘ���a. ����猧����MOS��ȫ�¾��_���ܘ�������Ч�ӹ��ʹܖ���ݵ�ͬ�r���o�B������ȫ��ؓ�d���գ�b. ��Դ�Qλ�·������ݔ��늉��^�_�r�����پ��_�Qλ�`��Ŵ�����ݔ��늉����ޣ���LDO�����^�pС������B�������������g���OӋLDO�ڃH����8.2��A�ėl���£����F��41ps��Ʒ�|��ͬ�r���l˲�B�r��ݔ��늉������^���l˲�B��ȃH������40%���͇��H���M�о�ˮƽ��ȣ��ڸ��ٵ���푑��Ͼ������@���ݡ�

���ν��ڣ����ʰ댧�w픕�ISPSD TPC���A��-��ӿƴ�����Ӽ��g�ό���Ҽ��gί�T��ί�T�����о�С�M��ע�ڸ��l�߹����ܶȼ����·�cϵ�y�о��������͉��������늡����ܹ��������ӡ����ܶȸ��x�Դ��Ƭ��LDO�ȡ�����/�Г���헇������c�аlӋ���n�}����Ȼ�ƌW�����Ŀ���Լ��A�顢�A���ȘI����Ҫ�M���n�}����IEEE JSSC��TCAS I/TCAS II��TPE��TIE��ISPSD��CICC���·��Ş�ڿ���피���h�ϰl��Փ��20��ƪ���W���V�������A�顢MPS��ʿ�m���Ї�늿Ƽ��F��Silergy��˼���֡�ʥ���ȼ����·���c���I��λ��

Փ��朽ӣ�https://ieeexplore.ieee.org/document/10233212

�������� ��/�����ˣ����Ԅ� ��/���l����ꐂ�